# **TI 59-58 hardware annotations**

### Introduction

This is the annotation file that accompanies the TI59/58 hardware diagrams available on my web-site http://xgistor.ath.cx

This information is based upon material written in Dutch by M.B. van der Mark in 1982. This material was made as a school project at the time. I have never met Mr. van der Mark but I suspect that I am following his wishes if I preserve his legacy for future generations, by making it available on the world wide web. His thesis did not contain any legal or other restrictions for me not doing so.

Initially I will not translate all the material he has provided in this thesis, just the bare bones of the TI59 operation and a description of the signals, timings and some other internals, revamped by color full and comprehensible diagrams and what ever I can phantom myself but what was not directly obvious from the source material.

However, my rule of thumb for now is that I will write only about things I understand, this because some of the original information was put down in a somewhat ambiguous fashion with some loose ends that I cannot resolve at this moment. M.B. van der Mark occasionally referred back to previously written material that I have no access to right now.

The annotation and the diagrams for the PC100 printer will be available (soon) in a separate set of files.

Anybody who is willing and able to provide additional material is invited to provide me with such and I will further process all material and make revisions on this information, to be put in the public domain as soon as reasonably possible.

Eventually I would also like to enhance this material with stuff about the "**HIR-commands**" and things like "**Fast-mode**" and "**Hex-programming**". If you have any of this please let me know.

My ultimate goal would be to gather and concentrate enough information to enable a group of people to write a comprehensive emulator for the TI59/58. This would preserve this beautiful vintage calculator -in a virtual manner- for our offspring in the eons ahead.

Sipke de Wal Springty 41 2201 WG Noordwijk Netherlands Email:sipke@wxs.nl

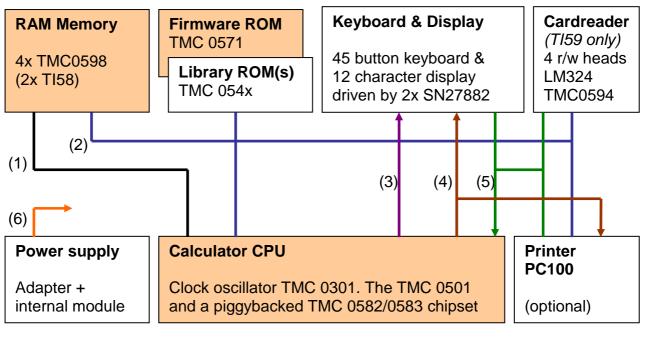

## TI59/58 Block Diagram

**Busses:**

I/O-1,I/O-2,I/O-4,I/O-8

IDLE, φ1 & φ2, EXT, IRG

SA ... SG + DPT

D0 ... D15, (L0 ..L12)

KN ... KT

Vss, -Vbat, Vdd, Vgg (input/output designation with respect to the CPU)

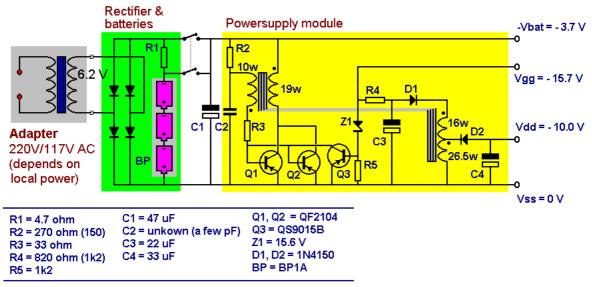

I suspect that all the TMC-chips are PMOS-technology, this based on the fact that they all require special extra negative power supply with respect to the main battery power. There is a thick-film power module in the calculator that provides for these extra voltages.

Warning! Since this power module does not contain any kind of voltage regulation I strongly advise you <u>not operate the calculator without the battery package</u>. The output of this power module may run out of control and may generate voltages that the PMOS-chips may not survive! In effect the batteries themselves act like a voltage regulator. (This is a feature of many calculators from the PMOS era, so be warned!)

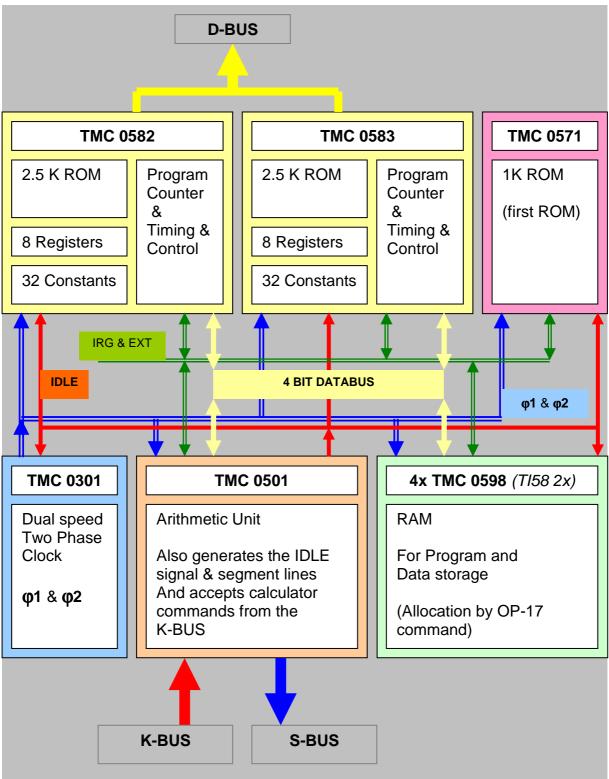

Before we'll cover the block diagram we'll need to know more about the role of the individual chips that form the processing core of the calculator. In the above diagram shown as the shaded parts. The rest of the machine can be regarded as peripheral devices with respect to the CPU-core. To understand it's operation we need to examine what functions are actually implemented in the core and how they are interwoven by the various types of signals.

Based on the above diagram we may conclude there are two sets of signal-busses in the TI59.

- The Data&Control-bus that glue the chipset together and additionally interfaces with the library-ROM, the Card Reader and the Printer. Most of the "internal" data and instructions are transmitted serially only the numerical data and the userprogramming code are exchanged between the CPU and the RAM-chips by means of a 4-BIT unidirectional data bus.

- The D-, S-, K-Scanning busses interface with the keyboard and the LED-Display. By way of exception one of the K-lines (KR) is used as a BUSY line that is utilized by the Card Reader and the Printer to indicate their busy-state to the CPU.

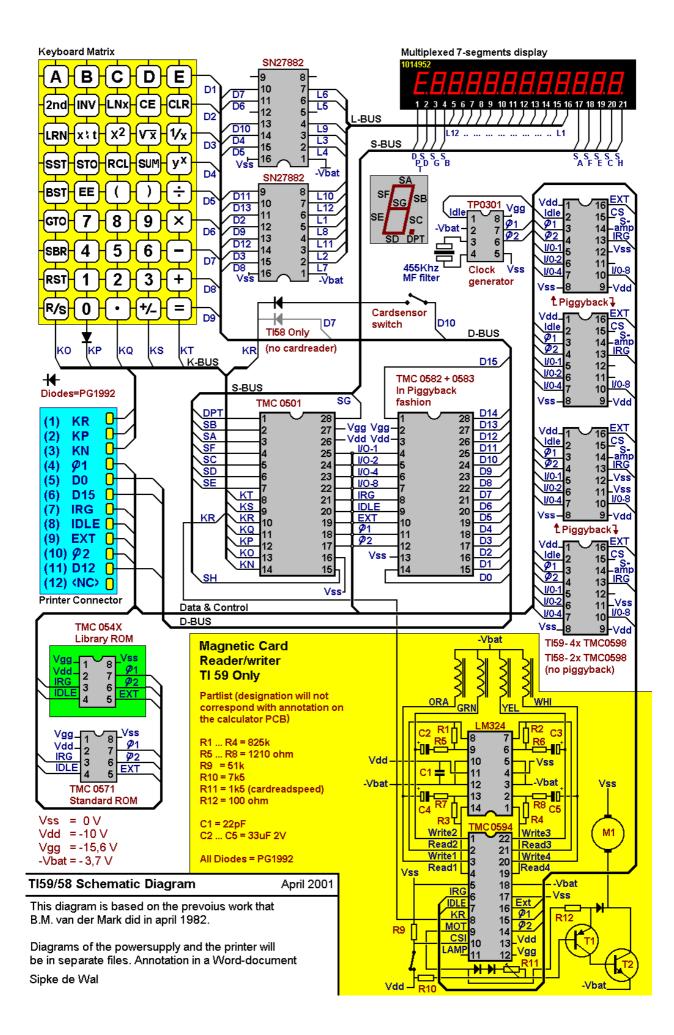

The previous page shows a small version of the TI59/58 diagram (A larger version is available at my web-site)

### **Busses:**

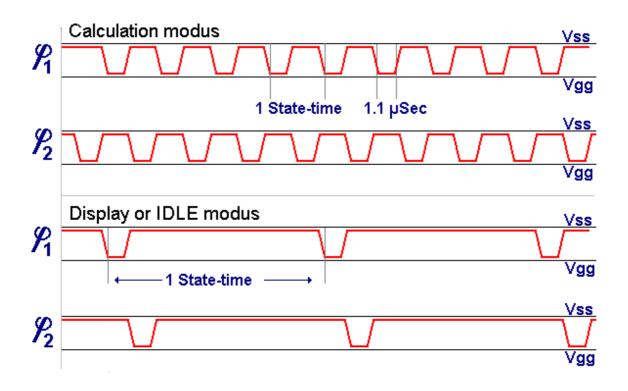

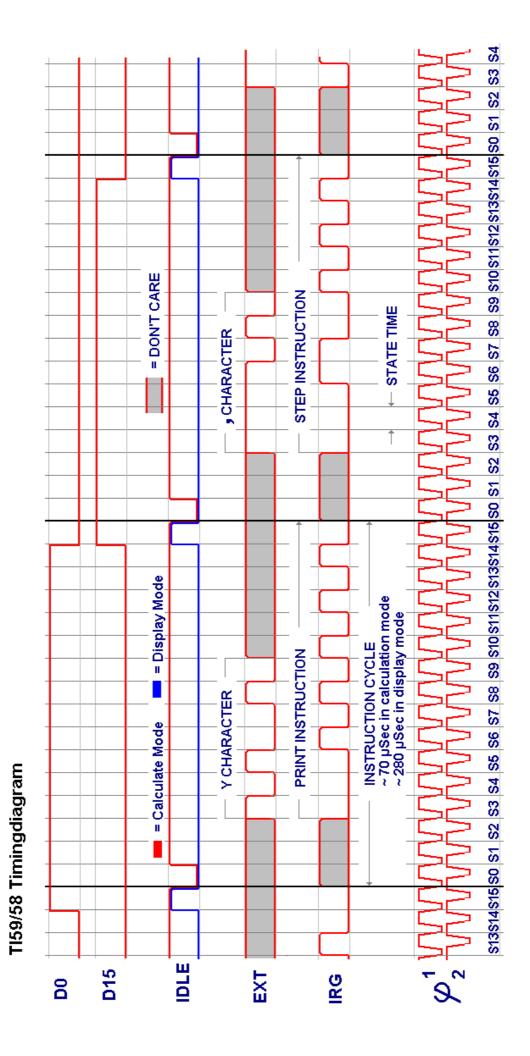

| Data & Control | φ1 & φ2 Clock | This is a 2-phase (non-overlapping) clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Vss-         |  |  |  |  |  |

|----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|

|                | signals       | <ul> <li>that switches between Vss and Vgg. It is derived from a 455 KHZ MF filter through the TMC0301-chip but some models of the TI59 have deviating ratings like 462 KHZ. The Clock operates in two modes.</li> <li>Calculating (full speed)</li> <li>Display or IDLE-mode (low speed) A Clock pulse is active at the negative Vgg level and each pulse takes 1.1 μSec. Then in IDLE-mode there is a pause of 3 cycles of the clock (See timing diagram) The period between two succeeding leading edges of φ1 are defined as a "State Time". 16 State-times make up and instruction-cycle. The first State-time of such a cycle is designated S0. Then S1, S2, S3</li> </ul>          | Vgg<br>(out) |  |  |  |  |  |

|                | IDLE          | S2, S3<br>IDLE indicates when the Arithmetic CHIP is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |  |  |  |  |  |

|                |               | finished with operations and a result is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Vdd          |  |  |  |  |  |

|                |               | displayed. IDLE switches between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (out)        |  |  |  |  |  |

|                | IRG           | Vss and Vdd. IDLE will always assert<br>negative at the start S0. If trailing edge of<br>IDLE goes up during S1 then the calculator<br>is in <u>Calculating mode</u> and works at full<br>speed. If the trailing edge of IDLE goes up<br>at S15 this will then indicate that the<br>Calculator is in <u>Display or IDLE-mode</u><br>This alteration of speeds facilitates longer<br>pulses on the D-Scanning lines at display-<br>time in order to make results more visible<br>and also minimizes the power use of the<br>CPU while the LEDs draw the most of the<br>current. This evening out power use at all<br>modes of operations.<br>This is the serial instruction line. Although | Vss-         |  |  |  |  |  |

|                |               | there are 16 bits transferred during S0 –<br>S15 only the bits during S3-S15 are valid<br>(S3=LSB). The first 2-bits are "DONT-<br>CARE" The definitions of the instruction<br>codes are described later on, in a couple of<br>tables.<br>IRG is a unidirectional (tri-state) line that<br>switches between Vss and Vdd                                                                                                                                                                                                                                                                                                                                                                   | Vdd<br>(3ST) |  |  |  |  |  |

|                    | EXT                     | This is the serial data line. It functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Vss-                   |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

|                    |                         | similar to the IRG-line but valid bits are only<br>transferred during S3 – S9 (S3=LSB)<br>It also is unidirectional and also switches<br>between Vss and Vdd. The EXT-line will                                                                                                                                                                                                                                                                                                                                                                                                                           | Vdd<br>(3ST)           |

|                    |                         | transfer several types of data between the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |

|                    | I/O-1, I/O-2,           | chips and character data to the Printer.<br>These lines transfer BCD-digit data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Vss-                   |

|                    | I/O-4, I/O-8<br>Databus | between the CPU and the RAM-chips. It<br>could in principal transfer a few HEX-codes<br>as well but there is not a lot of<br>documentation on this. During the S0-S15<br>state-times (1 instruction cycle) a full 16-<br>digit value can be transferred. Likewise 8 2-<br>Digit user-programs steps can be<br>transferred (See Value-representation<br>Diagram) These lines switch between Vss<br>and Vdd and are tri-state                                                                                                                                                                               | Vdd<br>(3ST)           |

| Scanning<br>busses | D0-D15                  | The are the Scan-send-lines. During<br>subsequent instruction cycles each of the<br>D-lines will go high (Vss) and stay high<br>during that instruction cycle until S14.<br>However, the leading edge of the D-signal<br>will start during S15 in the previous<br>instruction cycle The D-Lines scan the<br>keyboard and some will be buffered to drive<br>the Display LED-digits. (L-Bus). The D-lines<br>will switch between Vss and Vdd, they are<br>output only.                                                                                                                                      | Vss-<br>Vdd<br>(out)   |

|                    | L1 - L12                | Derived from D2 –D13 these lines are<br>buffered by 2 SN27882-chips to enhance<br>the power output of the scan lines in order<br>to drive the Display LED-digits. They switch<br>between Vss and –Vbat                                                                                                                                                                                                                                                                                                                                                                                                    | Vss-<br>-Vbat<br>(out) |

|                    | KN – KT                 | These are the Scanning-return-lines with<br>the exception of KR. They will connect to a<br>D-line when a key is pressed on the<br>keyboard and some extra K-lines are user<br>as jumper or switch lines for special<br>functions like the card reader enable and<br>position switch and one to distinguish<br>between a TI59 and a TI58 (Card Reader<br>present or not) On some models a 1200<br>ohm resistor is placed in series with these<br>lines. Some connections between D & K<br>lines may lead to undocumented TI59/58<br>features like:<br>KQ-D15=Master Reset<br>KN-D5 D11= Fast Mode/Firmware | (IN)                   |

|           | BUSY (KR)        | This Scan-return line is in effect a BUSY<br>line for the Printer and the Card reader.<br>The rest of the machine will wait as long as<br>this line is held at Vss by a peripheral<br>device                                                                                                                                                    |                                                                                                                                                                                   |                               |  |  |  |  |  |

|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|

|           | SA – SH &<br>DPT | Segment-lines will drive<br>Display LEDs of each dig<br>the first led digit to displa<br>when the CPU is in calcu<br>TI59/58's and the TI58C<br>buffered by an extra tran<br>the output (remember the<br>high only one quarter sta<br>calculation mode). Althor<br>documentation was not of<br>suspect the Segment-lin<br>between Vss and –Vbat | git. SH only drives<br>ay the "[" symbol<br>ulation mode. Some<br>c have this line<br>sistor to enhance<br>at the D-lines are<br>ate-time on during<br>ough my<br>clear on this I | ???<br>Vss-<br>-Vbat<br>(out) |  |  |  |  |  |

| Power bus | Vss              | From Battery                                                                                                                                                                                                                                                                                                                                    | 0 Volt                                                                                                                                                                            |                               |  |  |  |  |  |

|           | -Vbat            | From Battery                                                                                                                                                                                                                                                                                                                                    | -3.7 Volt                                                                                                                                                                         |                               |  |  |  |  |  |

|           | Vdd              | From Power module                                                                                                                                                                                                                                                                                                                               | -10 Volt                                                                                                                                                                          |                               |  |  |  |  |  |

|           | Vgg              | From Power module                                                                                                                                                                                                                                                                                                                               | -15.7 Volt                                                                                                                                                                        |                               |  |  |  |  |  |

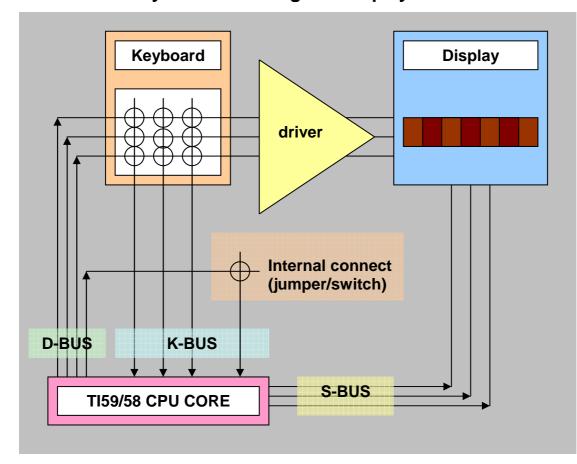

The following diagram shows a simplified representation of the way the calculator is wired (power, card reader and printer connections are not shown)

## Abbreviated keyboard scanning and display drive circuit

### $\phi$ 1 & $\phi$ 2 Clock timing diagram

Below a small version of the TI59/58 Power supply diagram. (A larger version is available at my web-site)

Sipke de Wal, April 2001

## The Scanning ROMs

The table below shows the RAM-registers in the scanning ROMs. Beside RAM, the Scanning ROMs also contain 32 Constants in ROM and 2.5Kb ROM each.

"First ROM" is a part of the firmware (TMC 0571). "Second ROM" is the Library ROM: the First ROM -being equal to the Library ROM in connection method- contains part of the preprogrammed functions (Op functions) while the ROM in the scanning ROMs contain code for more primitive functions as a micro-code for the Arithmetic-chip.

|                   | Digit | 15                                                  | 14               | 13         | 12                 | 11                                                  | 10        | 0                | 0                  | 7                                                   | 6                  | 5          | 4                  | 3                 | 2                    | 1                    | 0                   | 1                                          |

|-------------------|-------|-----------------------------------------------------|------------------|------------|--------------------|-----------------------------------------------------|-----------|------------------|--------------------|-----------------------------------------------------|--------------------|------------|--------------------|-------------------|----------------------|----------------------|---------------------|--------------------------------------------|

|                   |       | 10                                                  |                  | User F     |                    |                                                     | <b>10</b> | <b>9</b>         | <b>8</b>           | -                                                   | o<br>Addres        | -          | 4<br>Byte          | Prog              | Z<br>Last            | 1                    | Fix                 |                                            |

| TMC0582 Registers | 0     |                                                     | 10               | USEIT      | lays               |                                                     | 0         | 0                | 0                  |                                                     | nd ROM             |            | Dyte               | SRC               | Key                  |                      | ptd                 |                                            |

| iste              | 1     | Manti                                               | ssa              |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   | Expor                | nent                 | Sign                |                                            |

| eg                | 2     | ĺ                                                   |                  |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   | •                    |                      | 5                   | Ŧ                                          |

| Ř                 | 3     | ĺ                                                   |                  |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   |                      |                      |                     | era                                        |

| 82                | 4     | ĺ                                                   |                  |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   |                      |                      |                     | rc                                         |

| ŏ                 | 5     | 1                                                   |                  |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   |                      |                      |                     | ٧٢                                         |

| ž                 | 6     | 1                                                   |                  |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   |                      |                      |                     | Sta                                        |

|                   | 7     | 1                                                   |                  |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   |                      |                      |                     | Hierarchy Stack                            |

|                   | 8     |                                                     |                  |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   |                      |                      |                     |                                            |

|                   | 9     | List of data<br>flag                                | 0                | 0          | 0                  | 0                                                   | 0         | 0                | 0                  | 0                                                   | Current<br>Page    |            | New<br>Page        |                   | Security<br>Code     | No of ROMs           | No of prog<br>banks |                                            |

|                   | A     |                                                     |                  |            |                    | RA                                                  | M or C    | ONST             | ANT R              | OM PR                                               | OGRA               | MCOD       | ES                 |                   |                      |                      |                     |                                            |

|                   | В     | T-RF                                                | GISTE            | R          |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   |                      |                      |                     |                                            |

|                   |       | Manti                                               |                  |            |                    |                                                     |           |                  |                    |                                                     |                    |            |                    |                   | Expor                | nent                 | Sign                |                                            |

|                   | С     | PC                                                  | OP               | PC         | OP                 | PC                                                  | OP        | PC               | OP                 | PC                                                  | OP                 | PC         | OP                 | PC                | OP                   | PC                   | OP                  |                                            |

| TMC0583 Registers |       | 1                                                   | 1                | 2          | 2                  | 3                                                   | 3         | 4                | 4                  | 5                                                   | 5                  | 6          | 6                  | 7                 | 7                    | 8                    | 8                   | Opcode & Par. Count<br>for Hierarchy stack |

| TMC0              | D     | Page in run                                         | 0                | 0          | 0                  | 0                                                   | 0         | 0                |                    | memor<br>address                                    | 5                  | max.       | memor<br>addres    | ,                 | No of<br>pending ops | Parentheses<br>count | Deg<br>Rad<br>Grd   |                                            |

|                   | E     | Level 6<br>RAM Address<br>Const &2nd ROM<br>Address |                  | Byte<br>NR | Prog<br>SRC<br>FLG | Level 5<br>RAM Address<br>Const &2nd ROM<br>Address |           | Byte<br>NR       | Prog<br>SRC<br>FLG | Level 4<br>RAM Address<br>Const &2nd ROM<br>Address |                    | Byte<br>NR | Prog<br>SRC<br>FLG | Cond. Rtn<br>Flag | Sup Rout             |                      |                     |                                            |

|                   | F     |                                                     | Addres<br>t &2nd |            | Byte<br>NR         | Prog<br>SRC<br>FLG                                  |           | Addres<br>t &2nd |                    | Byte<br>NR                                          | Prog<br>SRC<br>FLG |            | Addres<br>t &2nd   |                   | Byte<br>NR           | Prog<br>SRC<br>FLG   | No of SBR<br>levels | Sup Routine Stack                          |

#### **TI59 CPU-registers**